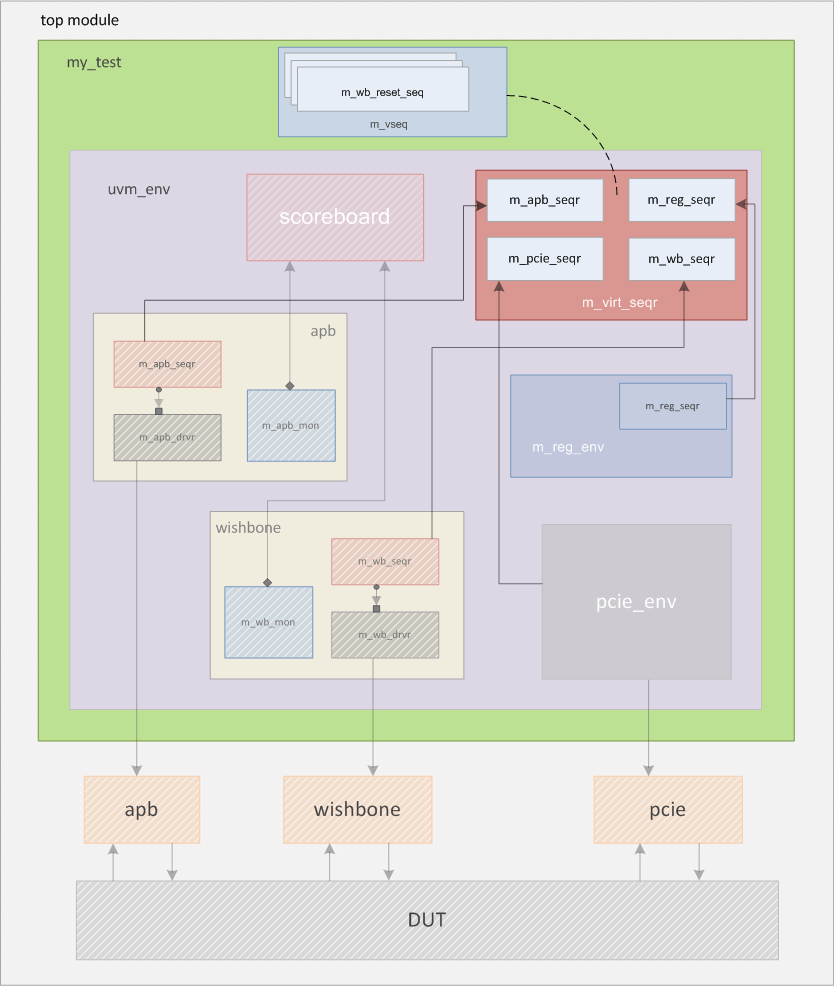

virtual sequence实际上是一个容器, 其中包含多个sequence, 这些sequence可以给不同env的sequencer发送激励。 比如Soc系统中有PCIe, wishbone, apb总线,一个比较好的方式就是使用virtual sequence进行控制:

如下图所示:

virtual sequence的使用示例如下代码所示:

1 | class my_virtual_seq extends uvm_sequence; |

档virtual sequence定义后, 可以在test case中这样去定义:

1 | class my_test extends uvm_test; |