虽然是做ASIC design的,但似乎有点必要学习一下UVM。 就逐步记录一下UVM中的一些重要的内容和学习笔记。 本篇就记录一下UVM phase的理解。

UVM phase简介

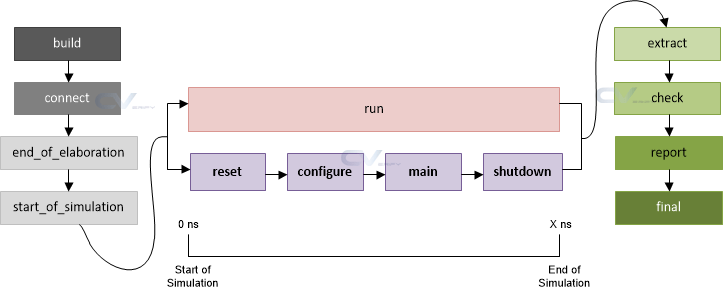

UVM的phase实际上提供了仿真过程的一种同步机制。可以大体上分成三种:

- Build time phases

- Run time phases

- Clean-up phase

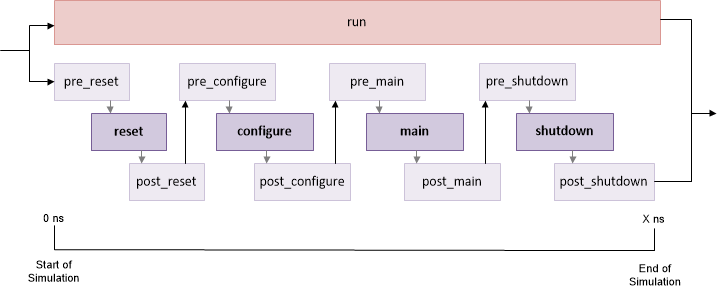

如下图所示:

对于function phase来说是不消耗仿真时间的, 而task phase消耗仿真时间。

下面分别介绍这三种phase:

- build time phase

- build_phase: function类型; 主要是实例化uvm_component

- connect_phase : function类型;通过TLM端口连接不同的uvm_componet;

- end_of_elaboration_phase : function类型; 显示uvm的拓扑结构和其他connection phase完成之后的函数;

- start_of_simulation_phase : function类型, 使用较少, 或者用于显示uvm结构

- Run time phases

- run_phase: task类型; 如上图所示, 和其他类型的run-time phase 并行执行。 driver 也是在这个phase开始驱动DUT

- Clean up

- extract_phase: function类型; 主要是从scoreboard中提取数据或者是关闭文件等;

- check_phase : 比较scoreboard和monitor观测到的数据;

- report_phase: 从checker 输出报告, 确认DUT是否通过测试;

- final_phase : 关闭co-simulation端口, 关闭文件等。

Build Phase

uvm的结构类似树形,因为要实例化很多的uvm_componets, 所以build phase的过程是从上至下的。

为了增加run phase的灵活性, uvm也提供了pre 和post phase, 如下图所示: