本篇主要介绍ASIC中的clock和SDC约束的方法。

创建clock

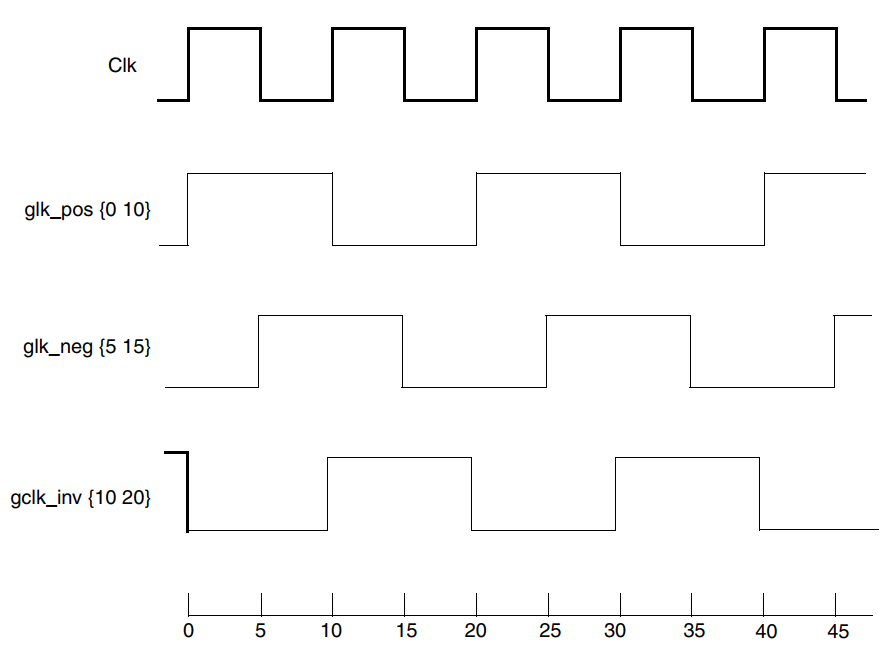

举一个例子, 如下如所示的clock 在SDC中如何产生?

sdc的约束可以像下面描述的:

1 | create_clock -period 5.0 [get_ports CK1] |

multiple clock

有clock MUX 存在时, 常常用exclusive clock 来约束:

1 | set_clock_groups -logically_exclusive -group {CK1} -group {CK2} |

也可以像这样指定多个clock group, 那么每一个group相对于其他group都是exclusive。

1 | set_clock_groups -logically_exclusive \ |

但是如果只指定了一个group, 那么这个group的clock 相对其他所有的clock都是exclusive:

1 | set_clock_groups -logically_exclusive -group {CK1 CK2} |

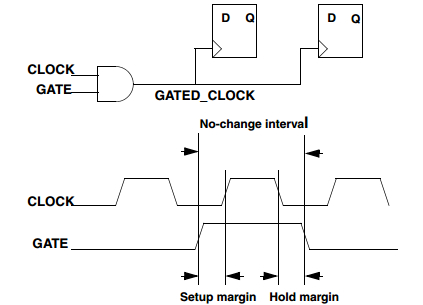

clock gating 检查

默认情况下, 工具不会检查clock gating 信号的setup和hold violation。可以使用set_clock_gating_check来进行检查:

1 | set_clock_gating_check |

如下图所示:

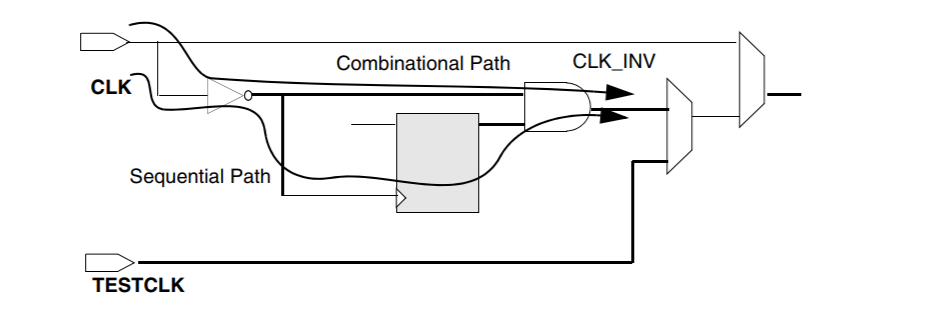

generated clcok

- 在STA的时候, 工具会通过combinational 和sequential两种PATH计算clock的latency。如下图所示:

如果在计算latency的时候想要Tool避开这些sequential PATH, 可以使用下面的约束:

1 | create_generated_clock -name CLK_INV \ |

- 再看一个非单边时钟约束的例子:如下图所示:

正沿的clock和负沿的clock都会穿过MUX, 所以可以在FF1的Q pin上有两个clock:可以用下面的约束方式创建:

1 | create_generated_clock -divide_by 2 -source \ |

-preinvert选项指的是源时钟反向, 而invert是gen clk反向。 区别如下图所示: