这篇文章中的大部分内容来源于其他blog, 我只是翻译和整理。 会在文章末尾给出原文章的链接。

在时序分析时, 常常遇到一个clock周期是另外一个clock整数倍的情况。 如果设置了multi_cycle_path 的话, Tool 会怎么check setup和hold timing?

慢到快的情况

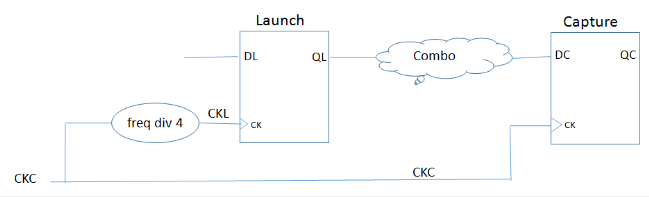

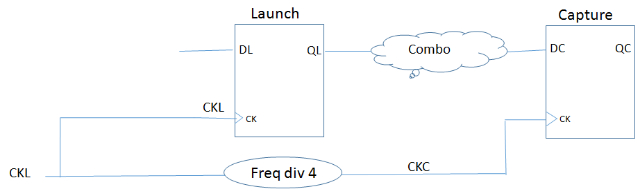

比如下面的电路:

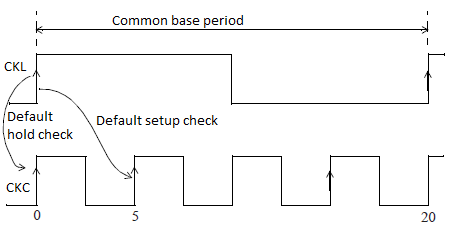

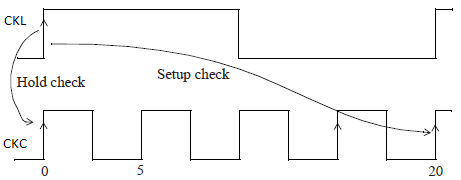

launch clock是capture clock的1/4, 这时候Tools 默认的setup和hold的check关系如下图:

但是这样check的话并不符合我们的设计意图, 因为期望的并不是在CKC的下一个沿check data, 而是第4

个沿。 因此要设置multi_cycle path的约束:

1 | set_multicycle_path 4 -setup -from [get_clocks CKL] -to [get_clocks CKC] -end |

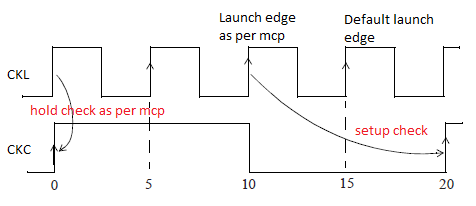

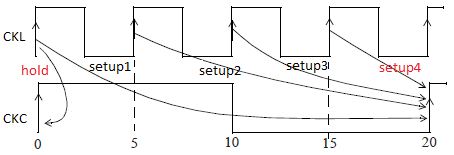

那么setup和hold的check 关系变成如下图所示:

如果不加hold 的约束的话, 那么hold的check 是在setup的前一个edge。 这样会造成很多的violation。所以应该加上:

1 | set_multicycle_path 3 -hold -from [get_clocks CKL] -to [get_clocks CKC] -end |

那么setup和hold的check 关系变成如下图所示:

在slow 到fast这种场景下推荐使用-end 选择来设置multicycle path。下面是PT中-end 选项的说明:

-end Indicates that the multicycle information is relative to the period of the end clock. The -start and -end options are needed only for multifrequency designs; otherwise, start and end are equivalent. The end clock is the clock source related to the register or primary output at the path endpoint. The default is to move the setup check relative to the end clock, and the hold check relative to the start clock. A setup multiplier of 2 with -end moves the relation forward one cycle of the end clock. A hold multiplier of 1 with -end moves the relation backward one cycle of the end clock.

快到慢的情况

如下图所示是fast clock 到slow clock的场景:

这时候Tool check timing 默认的行为如下图:

如果我们想让约束相对于快的时钟,放松2个cycle, 也就是说launch edge 在t =10, capture edge在t = 20。那么就需要增加下面的约束:

1 | set_multicycle_path 2 -setup -from [get_clocks CKL] -to [get_clocks CKC] -start |

其中 -start 选项说明如下:

-start indicates that the multicycle information is relative to the period of the start clock. The -start and -end options are needed only for multifrequency designs; otherwise, start and end are equivalent. The start clock is the clock source related to the register or primary input at the path startpoint. The default is to move the setup check relative to the end clock, and the hold check relative to the start clock. A setup multi-plier of 2 with -start moves the relation backward one cycle of the start clock. A hold multiplier of 1 with -start moves the relation forward one cycle of the start clock.

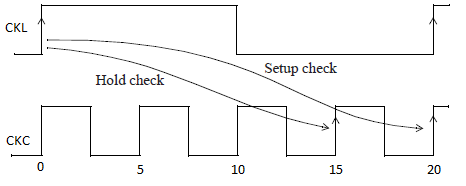

同样要设置hold 的multicycle 约束才能得到我们预期的check 行为:

1 | set_multicycle_path 1 -hold -from [get_clocks CKL] -to [get_clocks CKC] -start |

修改后的timing check关系如下图: